상세 컨텐츠

본문

※ Part. 1에서는 Oxidation Process가 어떤 것이며 Wafer 위에 올라가는 SiO2의 물성과 성장방법

그리고 그에 관련된 Kinetics와 공정에 중요한 영향을 미치는 Parmeter를 알아보았다.

서울대학교 반도체 공동연구소 공정실습 : Oxidation Process part. 1

1. Oxidation Process? 반도체 공정에서 사용하는 Thermal Processes 중 하나이며 우리말로 흔히 산화공정이라고 하는 Oxidation Process는 Wafer 제조 공정으로 만들어낸 고순도의 Si 기판에 H2O와 O2 같은 산화제

arranged.tistory.com

1. LOCOS와 STI 그리고 산화막의 다양한 용도

1. LOCOS

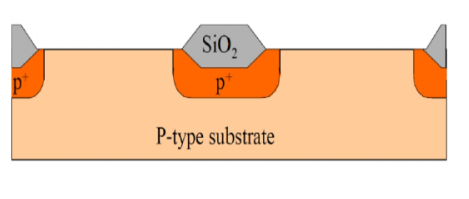

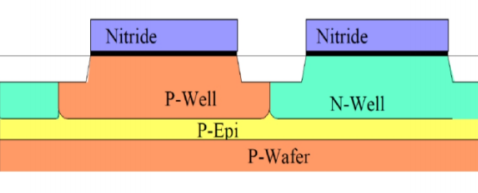

Transistor들의 간격이 미세공정이 진행됨에 따라 많이 가까워지고 있는데, 서로간의 불필요한 영향을 막기 위해서

Transistor 간의 Isolation이 필요하다. LOCOS는 전기적인 Isolation을 위해 등장한 방법이다.

LOCOS 는 Local Oxidant of Silicon의 줄임말로 물의 확산성이 낮은 소재를 이용한 마스크 산화방법이다.

이 방법은 흔히 SiO2의 선폭이 상대적으로 길 때 사용된다.

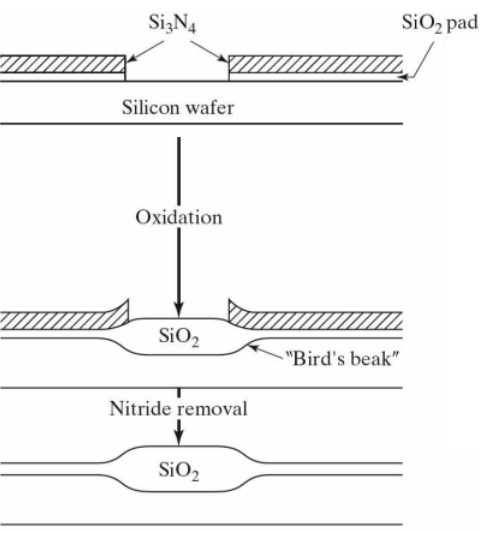

해당 방법의 순서는 다음과 같다.

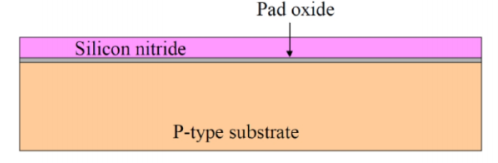

1) Si위에 Si3N4를 바로 덮으면 Stress가 발생하기에 먼저 Pad Oxide를 먼저 덮은 후 Si3N4를 덮는다.

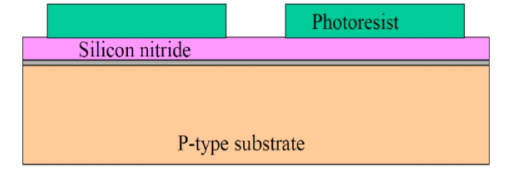

2) PR을 도포하고 노광과 현상을 진행한다.

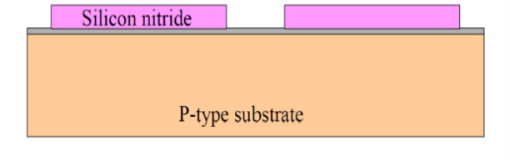

3) Si3N4를 Etching 하고 PR을 Strip한다.

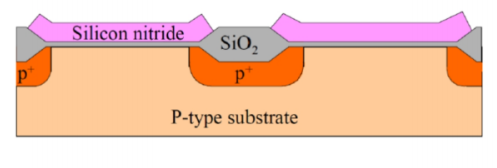

4) Isolation에 도핑을 진행한 후 열산화법으로 SiO2를 성장시키면 SiO2가 형성되는데, 이때 SiO2와 Si3N4의 TCE가

다르기 때문에 Bird's Beak(새부리 현상)가 형성된다.

5) Si3N4를 Strip하면 전기적으로 isolation된 구역이 정해져서 소자가 분리된다.

※ Bird's Beak: LOCOS를 이용하면 열 성장속도 차이에 의해서 노출된 부분의 가장자리는 덜 성장하고 중심부는 많이 성장하는 현상이다. 이러한 형상이 새부리의 모습을 닮아서 다음과 같이 불린다.

LOCOS 방법은 산화막이 Nitride 아래쪽으로도 파고드는 Bird's Beak를 형성하며, 이는 소자의 핵심적이 역할을 하는 Source와 Drain이 위치하는 Active 영역에 영향을 끼치게 된다.

소자가 미세화되는 현재의 추세에는 Active 영역에 미치는 영향도 커지기 때문에 LOCOS가 아닌 STI 기법을 사용한다.

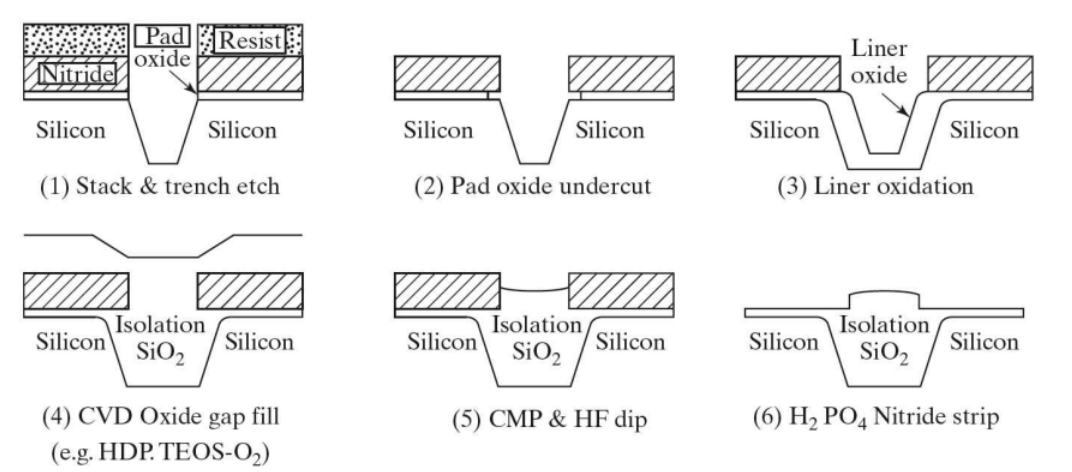

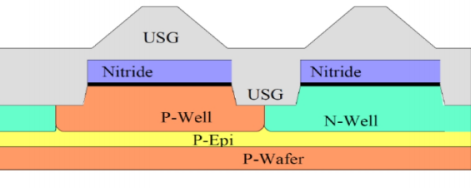

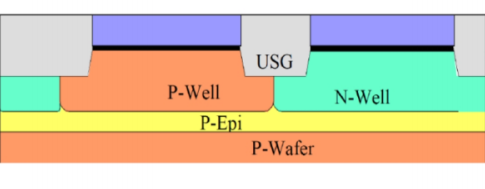

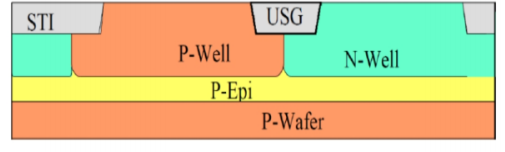

2. STI(Shallow Trench Isolation)

전체적인 공정은 다음과 같다

1) Shallow Trench Isolation은 더 깊게 SiO2를 만들 수 있어서 선포기 좋은 곳에서 사용한다.

2) PR 도포 후에 노광, 현상 후 Dry Etching으로 Si 내부까지 파내고, PR strip까지 진행한다.

3) Gap fill이 우수한 HDPCVD를 통해 USG(Undoped Silicate Glass) 증착

4) CMP로 평탄화 해준다.

5) Si3N4를 Strip한 후에 CMP로 평탄화하면 깊은곳까지 SiO2를 형성한다.

해당 방법은 CMP를 활용하기에 Over Polishing으로 인한 Si 표면의 Uniformity가 나빠질 수 있다.

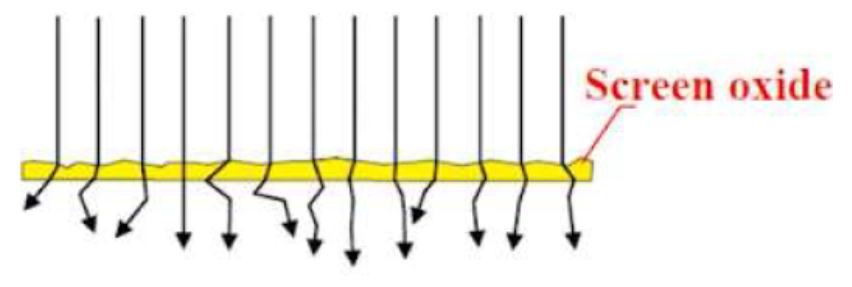

3. Screen Oxide Layer

Ion implantation process 진행 중에 높은 에너지를 가지는 Ion beam에 의한 실리콘의 표면손상을 방지하기 위해

사전에 성장시키는 보호막이다.

이는 Channeling 현상 또한 방지할 수 있다.

※ Channeling 현상은 가속된 이온이 결정구조의 빈 공간으로 원하지 않는 깊이까지 침투해버리는 현상이다.

이는 깊이에 대한 컨트롤이 되지 않기에 원하는 전기적인 특성으 구현하지 못하게 된다.

이를 해결하기 위해서 Wafer를 약 7도 정도 Tilt 하거나 Screen Oxide를 미리 덮어 표면을 비정질구조로

만들기도 하고 낮은 확산계수의 도펀트를 이용하기도 한다.

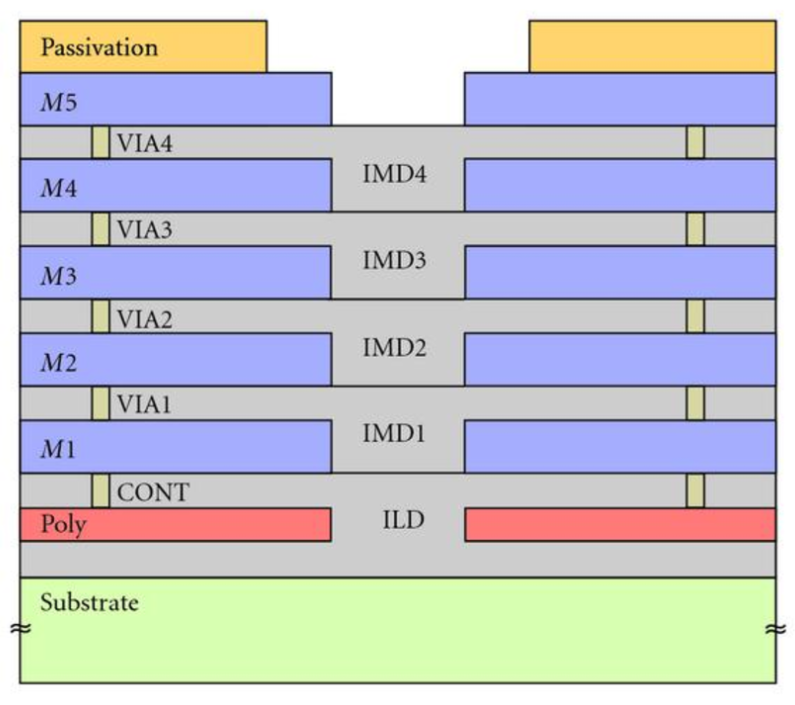

4. ILD, IMD, Passivation

1) ILD

ILD는 Inter Layer Dielectric의 약자로 Si와 Metal을 절연하는 역할을 한다.

2) IMD

IMD는 Inter Metal Dielectric의 약자로 Metal 간 절연하는 역할을 한다.

3) Passivation

Metal Layer를 보호해주는 역할을 한다.

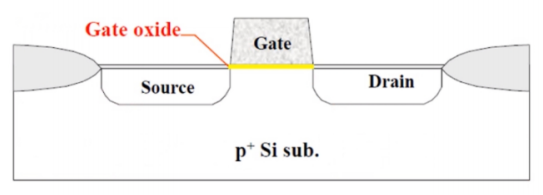

5) Gate Oxide

Gate는 우리가 흔히 볼 수 있는 Transistor에서 금속으로 제작되는 소자이다.

MOSFET이 Metal Oxide Semiconductor Field Effect Transistor의 약자인데 이때 Gate가 metal로 만들어진다.

Gate Oxide는 Gate와 기판 사이의 절연막으로 Source-Gate-Drain 간 절연을 하는 역할을 한다.

반도체 미세공정의 트렌드에 따라 소자들이 계속해서 작고 얇아져야 했으며 동작속도가 빠르고 전력소모가 적어야 하기에

기존의 SiO2의 절연효과를 가지는 물질을 매우 얇은 물질로 대체하기 위해서는 높은 유전율을 가지고 있는 소자가 적합하다고 판단되어 왔다.

하지만 얇은막 즉, 박막은 두꺼운 막에 비해서 전자보관성과 절연내구성을 위시한 안정성이 떨어지고 누설전류가 박막에

비해서 많다는 단점을 가지고 있다.

현재 Gate의 크기와 채널의 길이가 짧아짐에 따라 SiO2 to SiON to High k 물질로 바뀌어 왔다.

이를 HKMG(High-k Metal Gate)라고 한다.

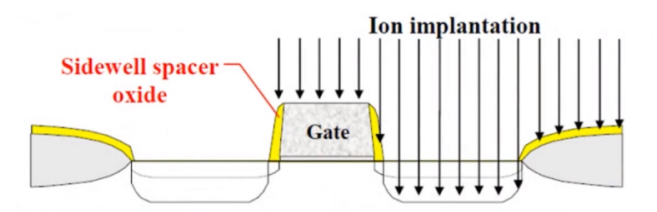

6) Side Wall Space

Gate 옆에 붙은 SiO2가 이온주입공정에서 기판내의 Dopant 주입을 막는 역할을 한다.

이때 Spacer 아래에 도핑된 LDD(Lightly Doped Drain)이 존재하는데, LDD는 Source to Drain간 강한 전기장에 의해 발생하는 Hot Carrier Injection 현상을 개선시킨다.

LDD를 유지하는 일종의 방어막으로 공정 순서는 다음과 같다

- Gate 와 Si 사이의 SiO2를 남겨두고 Mask를 이용하여 Si위의 SiO2를 제거해준다.

- 화학증기증착(CVD)를 이용하여 SiO2를 증착시켜 준다. 이때 Side Wall의 막 퀄리티는 소자 특성이 지대한 영향을 주지 않기 때문에 빠르게 증착할 수 있는 PECVD(Plasma-enhanced Chemical Vapor Deposition)을 이용한다.

- 이후 Dry Etching을 통해 Side Wall을 형성한다.

- 이온을 가속하여 높은에너지인 상태로 주입을 한다.

- 기존의 LDD위에 일정 부분 Side wall로 인해서 LDD보다 더 깊은 곳까지 주입된 부분과 그렇지 않은 부분이 나눠진다.

※ Hot Carrier Injection: Channel Length가 짧아지면서 Source to Drain으로 이동하는 전자가 더 높은 전계를 받게 된다.

높은 전계에 의해 에너지가 매우 높아진 캐리어들은 Si 기판과 충돌하여 Electron Hole Pair를

형성하고 형성된 EHP도 높은 전기장에 의해 가속되어 또 다른 EHP를 형성하는 Avalanche Breakdown을 일으켜 소자가 망가지게 된다.

이로 인해 Gate Oxide를 통과하거나 Channel 이외의 영역에서 Tunneling이 일어나면서

Gate Oxide의 Capacitance 값을 감소시켜 누설전류가 발생하거나 Threshold Voltage가 증가하는

악영향을 끼치는 효과를 말한다.

※ LDD: Lightly Doped Drain을 말하며 캐리어가 느끼는 전계를 감소시키는 공정이다. 이는 HCI를 해결할 수 있다.

Si-SiO2-Gate로 구성된 구조에서 약하게 Ion implantation을 진행하여 STI-SiO2-Si로 둘러싸인 구조 사이에

약하게 도핑을 진행하여 전계가 가장 강하게 걸리는 Junction Boundary에서의 도핑 농도를 줄이는 방법이다.

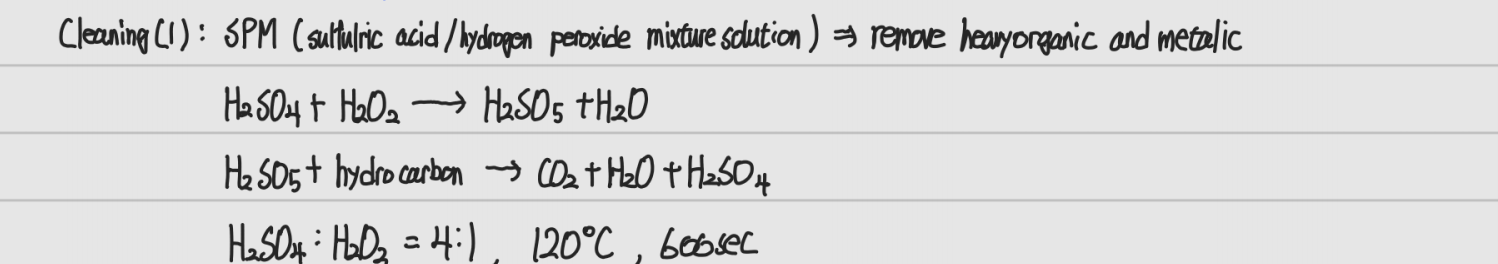

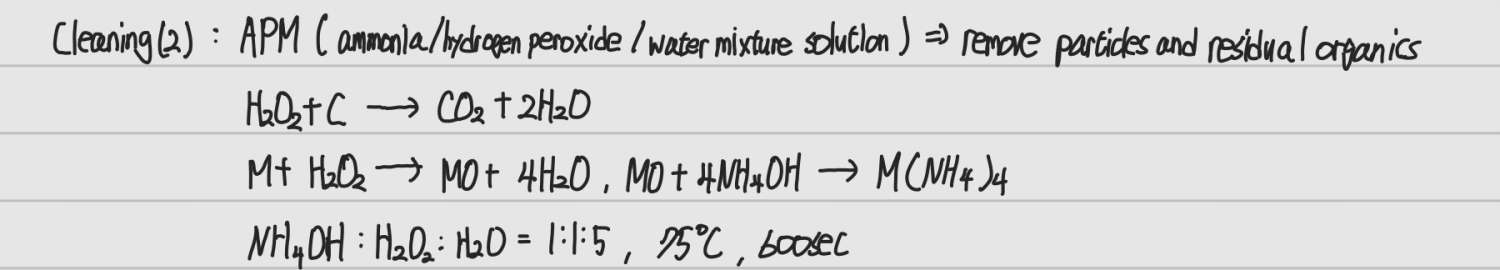

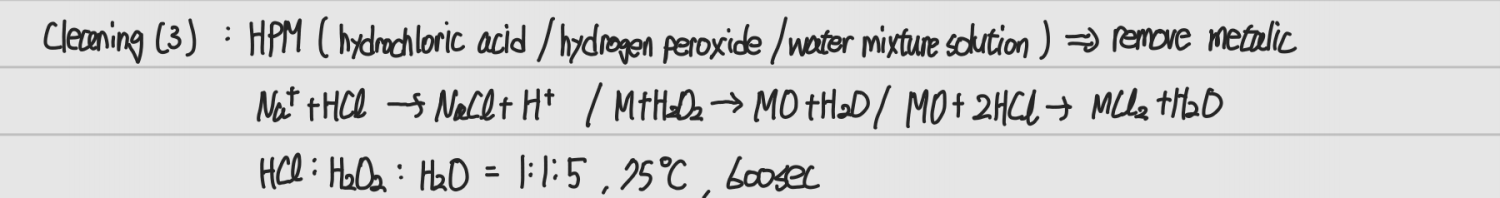

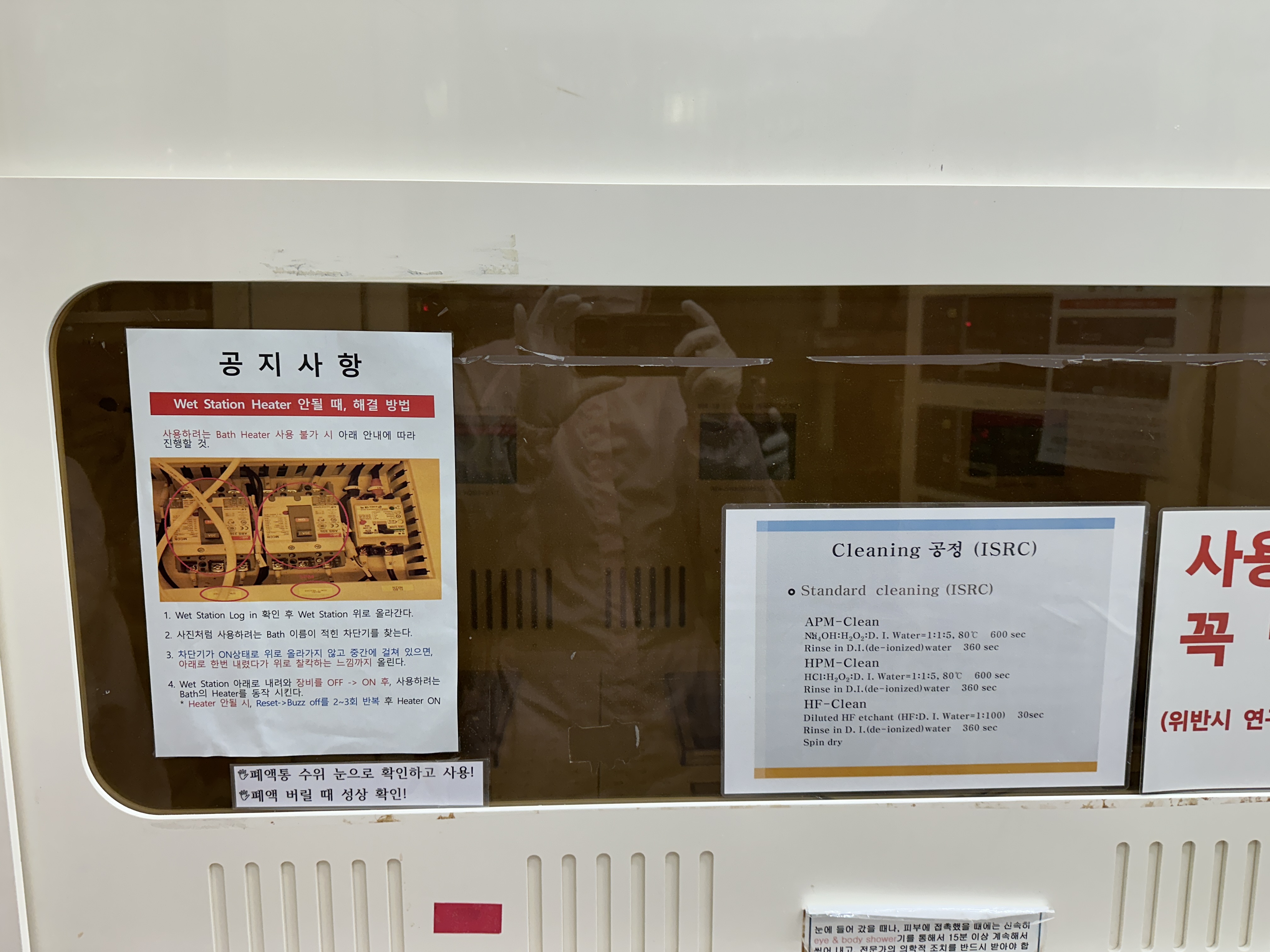

2. Cleaning 공정

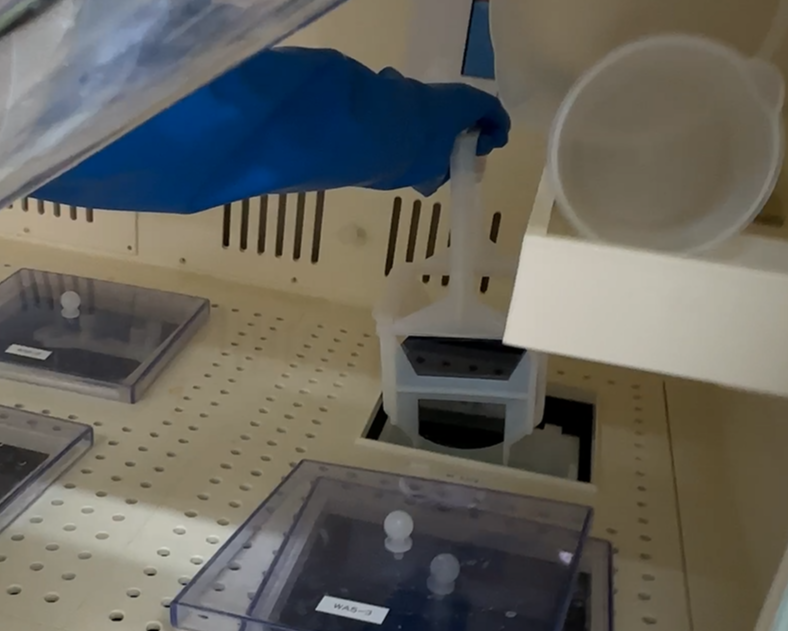

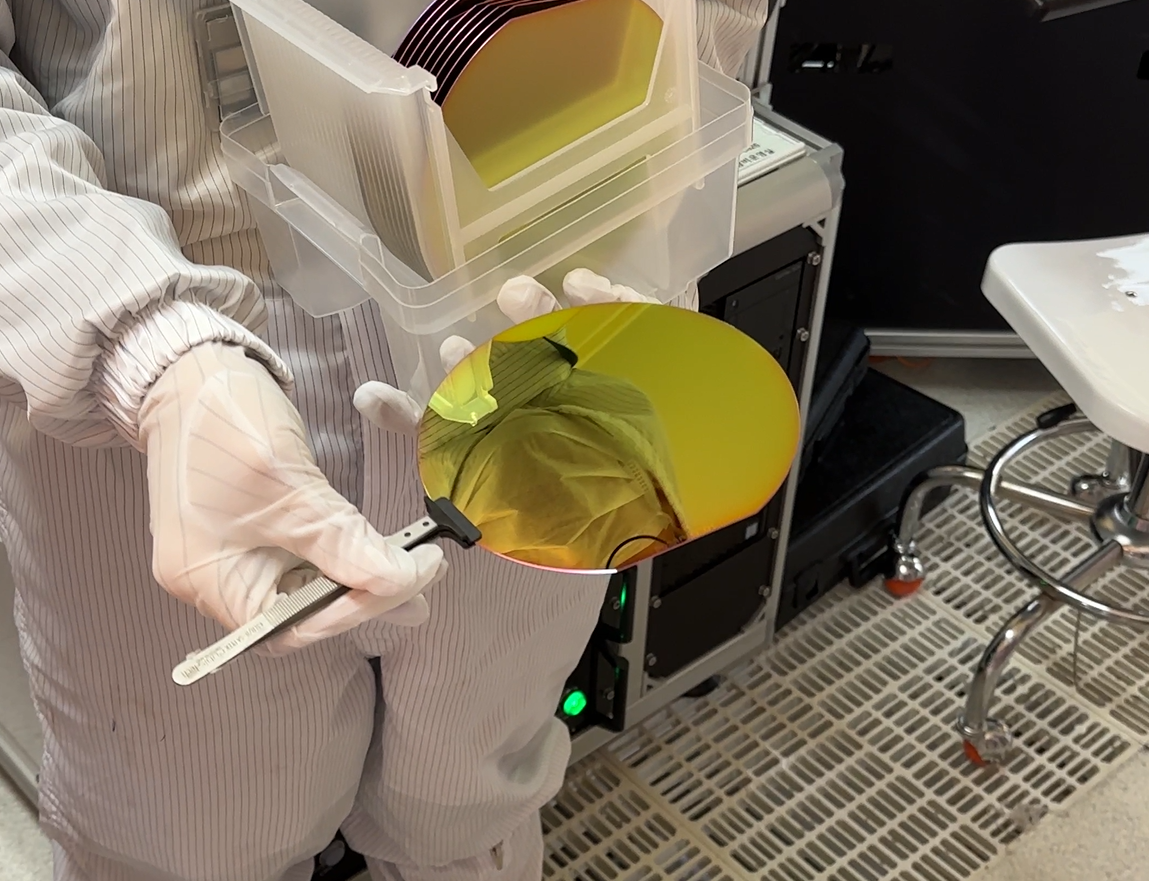

서울대학교 ISRC Fabrication에서 Cleaning Bath에서 Cleaning을 진행한뒤에

Furnace에서 Oxidation을 진행하고

Inspection 과정을 통해 데이터를 뽑아보았다.

Cleaning을 진행하지 않는다면 MOSFET에서 Mobile Charge(Na+)로 인해 Sweep하는 과정에서 Channel 형성을 돕게된다

이로 인해 Threshold Voltage가 낮아지고 IV Curve가 달라진다.

따라서 Mobile Charge 위치를 특정하기 위해서 온도를 올려 Voltage를 올리거나 내려 Threshold Voltage의 변화를 읽어야 한다.

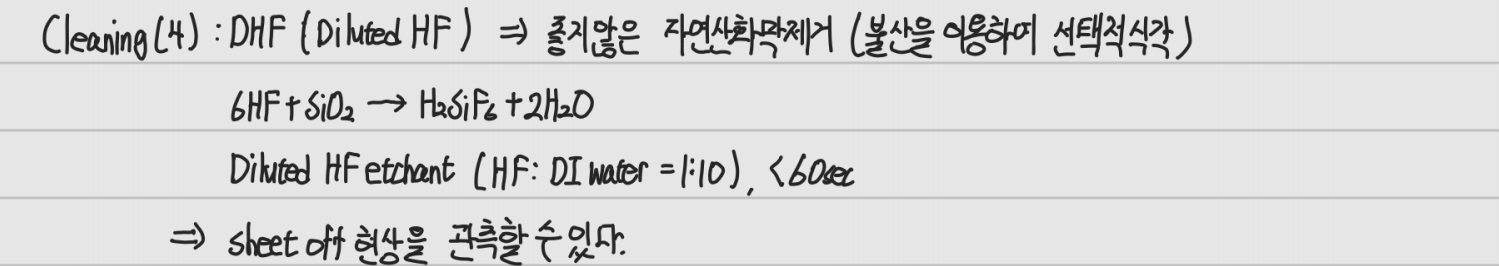

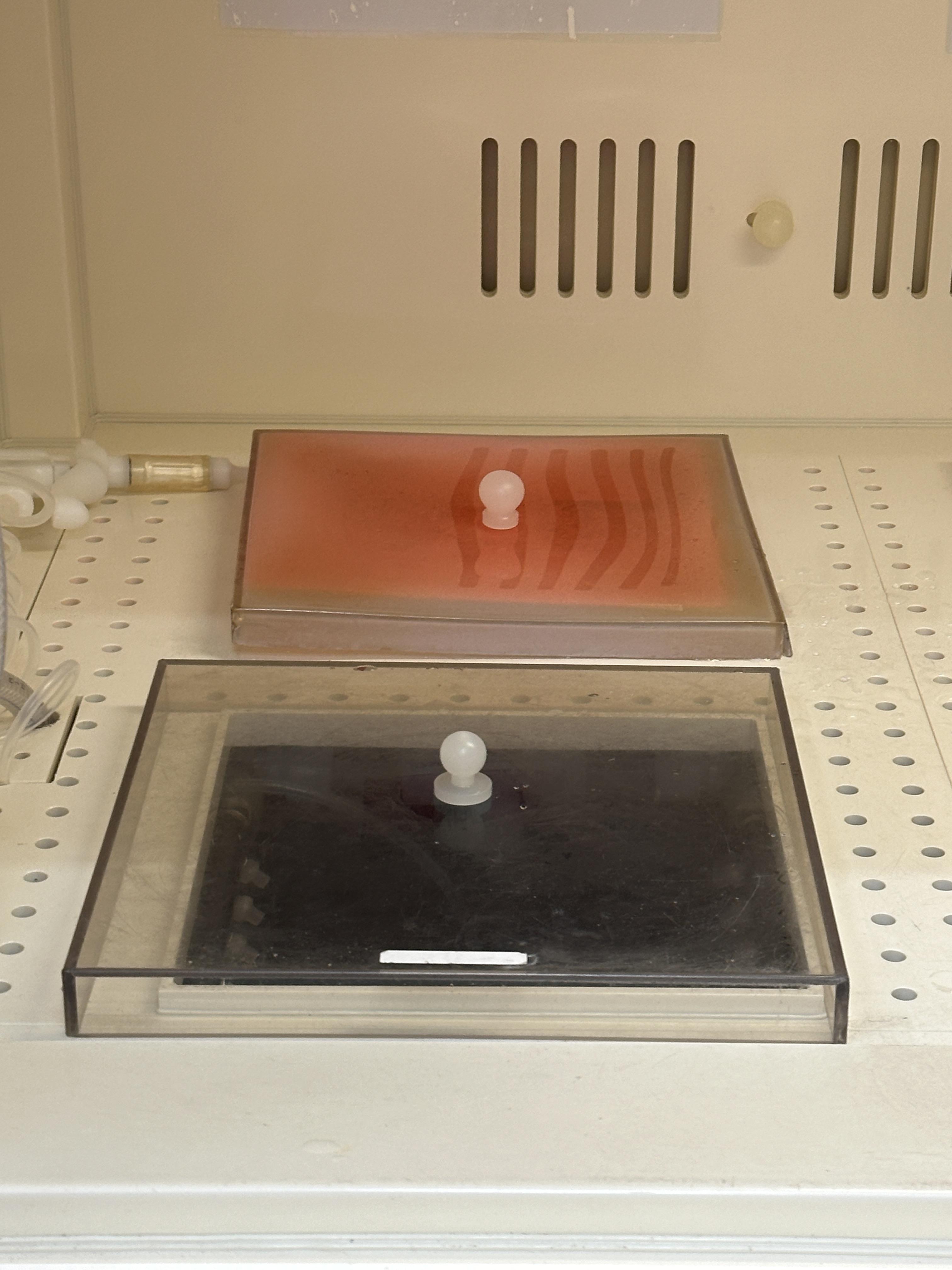

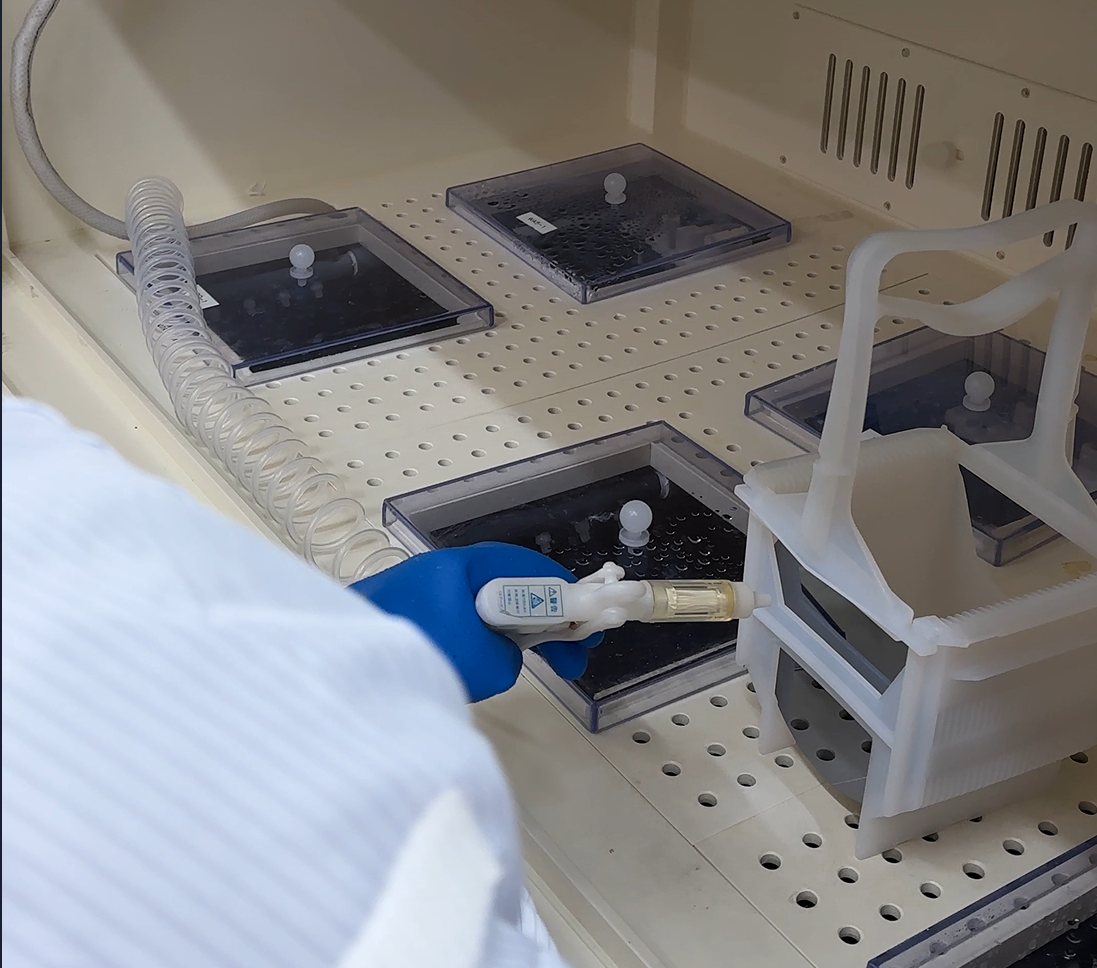

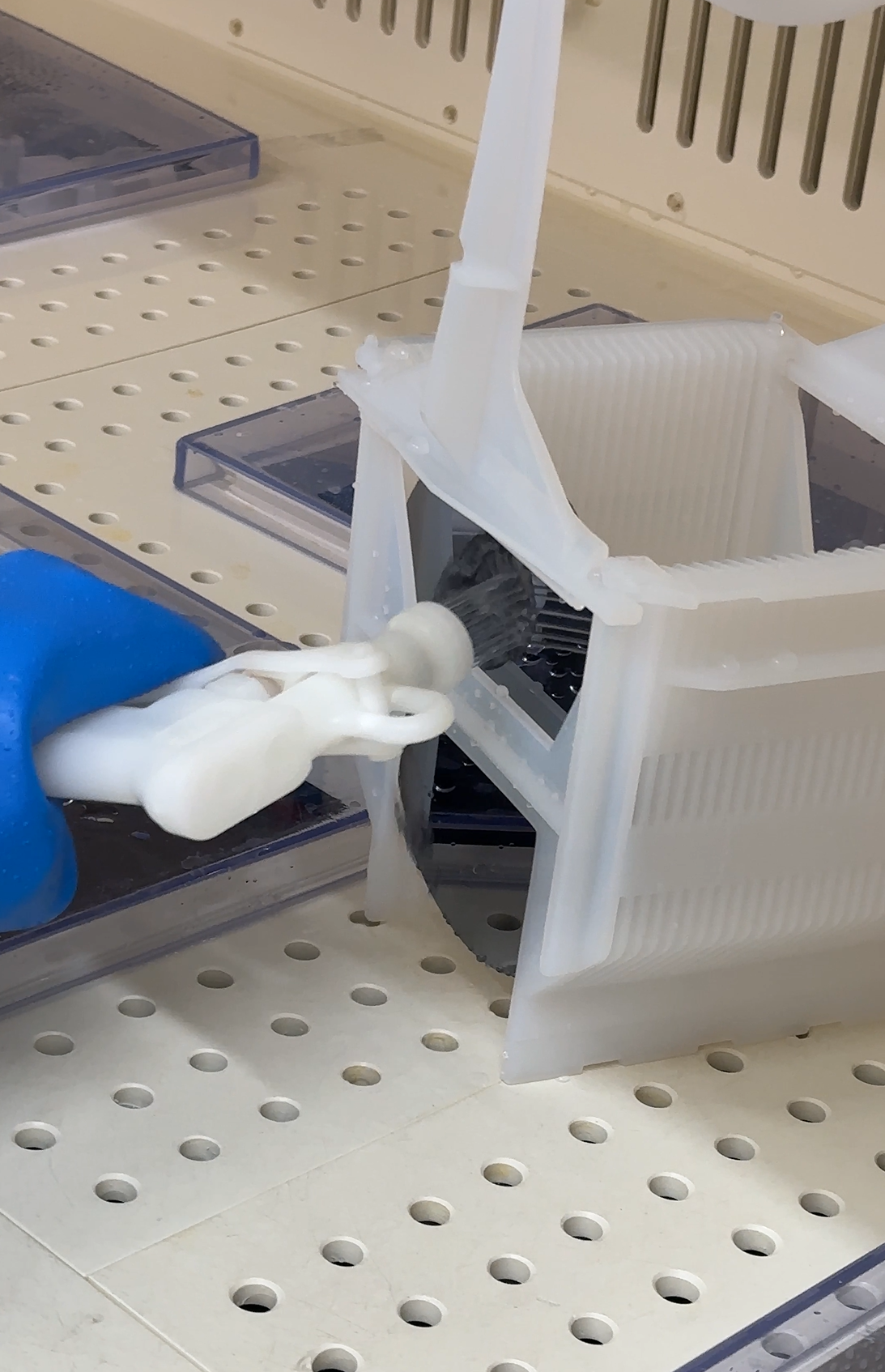

SPM 공정 후 QDR 공정(버블로 세척)

물이 맺혔던것과 상반되게 Wafer가 젖어있음을 알 수 있다.

이는 산화막이 친수성이기 때문에 산화막이 깔려 있음을 유추할 수 있다.

DHF 공정을 하기 전 Wafer에 DI Water를 뿌리면 Wafer가 젖어있음을 확인할 수 있다.

DHF 공정은 불산을 이용하기 때문에 안전장치를 착용하고 수행한다.

1초에 0.5~1nm 정도 산화막을 벗겨내며 SPM 으로 생성된 산화막을 벗겨내는데에 20초 정도 소요된다.

이때 산화막을 전부 벗겨내고 싶다면 다음과 같은 방법으로 해도 되나, 5000Å중 1000 Å 만 벗겨내고 싶다면

어차피 Sheet off이 관찰되지 않기 때문에 모니터 웨이퍼를 가지고 Etch rate을 계산해서 공정을 수행한다.

끝나고 QDR 공정을 통해 세척을 해준다.(Bath 마다 다른 물질들이 존재하므로 섞이는 것을 방지)

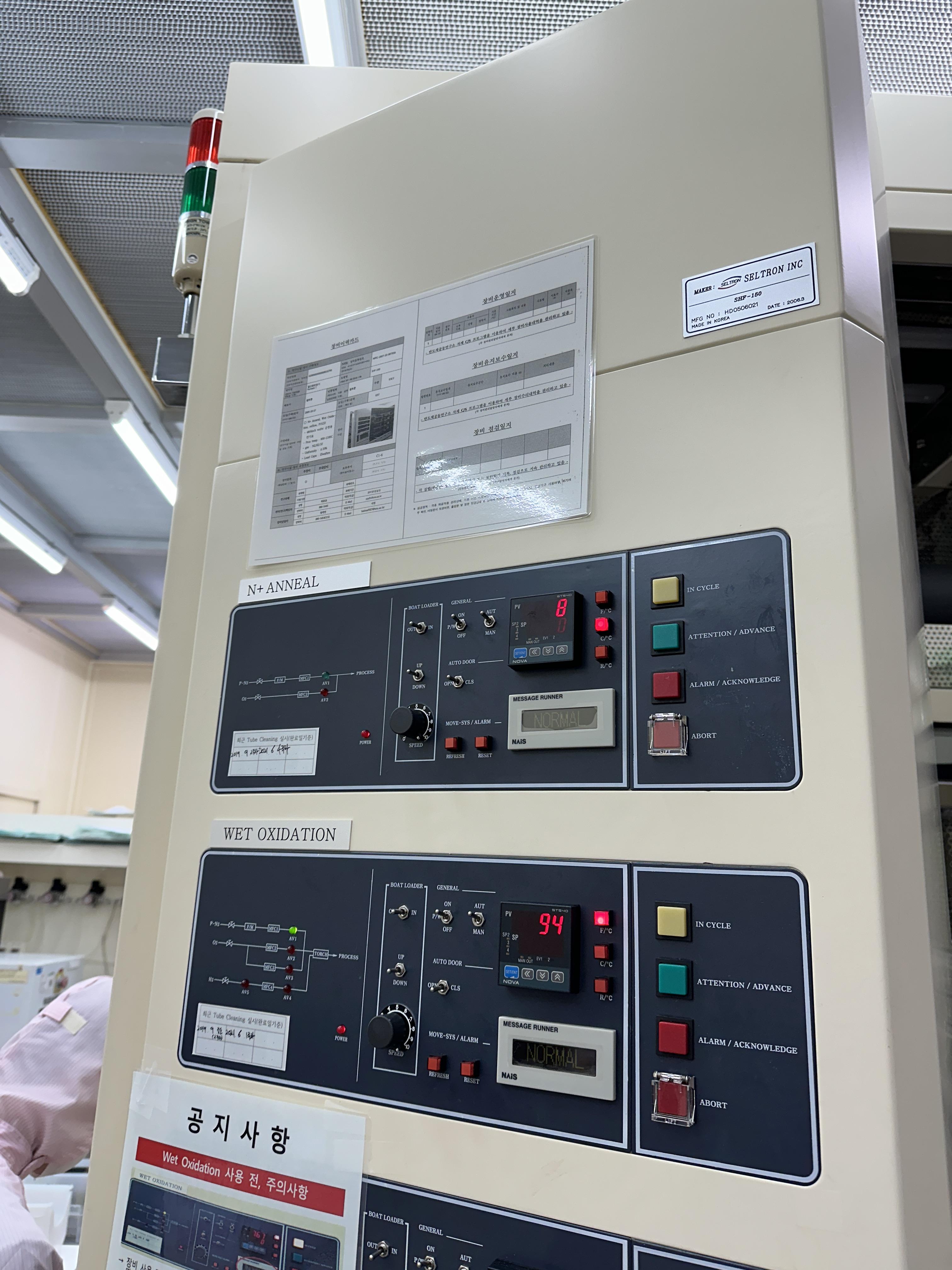

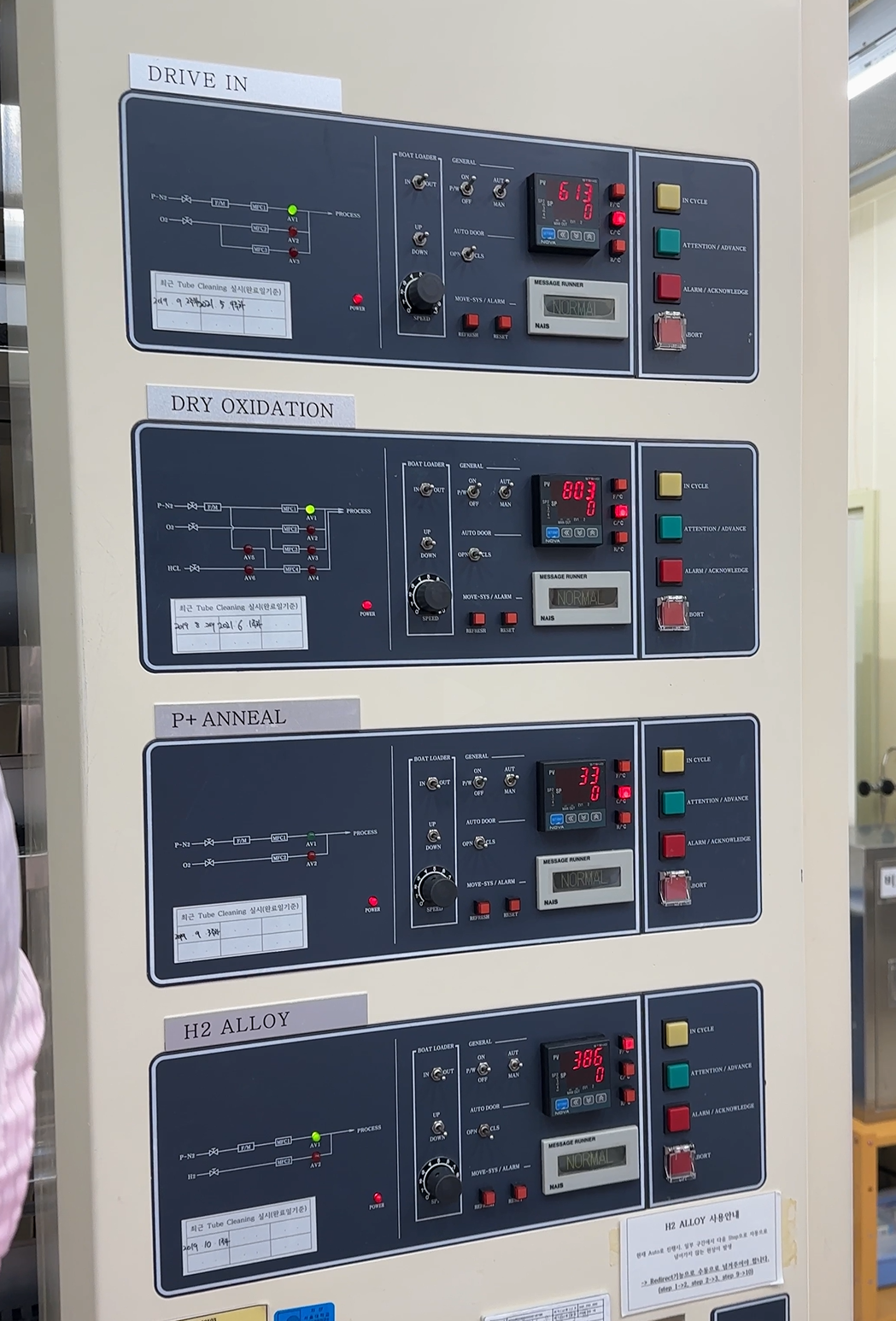

3. Furnace System

Furnace System은 Thermal Process에 다양하게 사용되는 장비이며 자세한 사용처는 다음과 같다.

- Wet/Dry Oxidation [이때 N2는 Tube내 유기물이 들어와서 타는 것을 방지해주며 O2와 H2는 Oxidant HCl은 산화막질을 개선해주는 역할을 한다.]

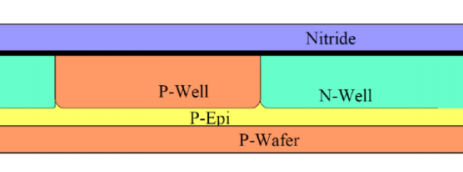

- Well Drive in: 단일 Wafer에 p-type과 n-type substrate를 형성한다.

- POCl3 Doping: Phosphor Silica Glass(Phosphorus로 도핑된 SiO2)로 열주기 동안 확산시킨 후 Silicon에 n-type로 도핑한다.

- Annealing: Ion implantation 등으로 주입된 불순물의 활성화 및 Si 재결정화로 recovery의 기능을 수행한다.

- H2 Alloy: Si 계면의 Dangling Bond로 인한 Interface Trap의 제거를 위해 수소가스를 주입한다.

- Reflow: 방울 방울 떨어져 있는 SiO2를 균일하게 펴준다.

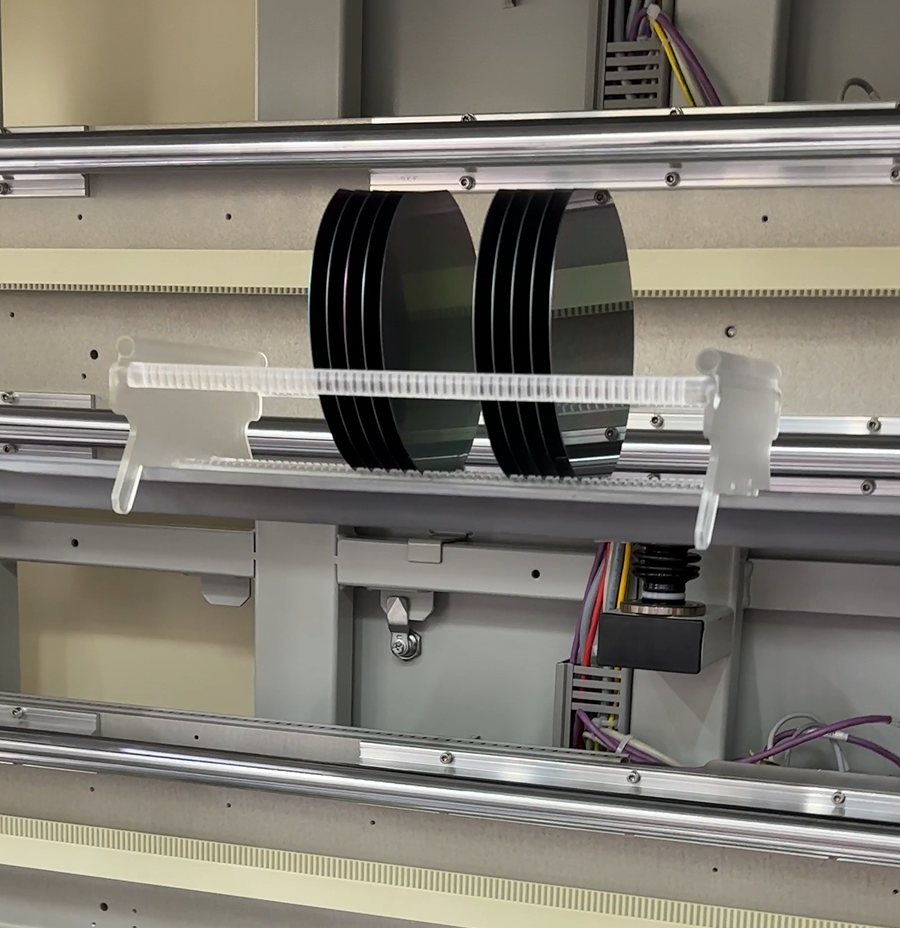

Furnace를 사용하기 위한 공정 조건을 Set up 해야 한다. 해당 사항을 다음과 같다.

- Dummy Wafer를 사용하여 방향에 따른 편차를 줄인다.

- Part 별로 온도를 다르게 하여 산화속도를 조절한다.

- Tilting하여 균일하게 열처리를 해야한다.

- 와류가 아닌 층류를 형성하기위해 Wafer를 규칙적으로 배열해야 한다.

산화막의 성장속도는 오도와 결정방향에 따라 다른데, Poly인경우 결정방향과 상관이 없는 CVD를 사용하며

결정방향과 상관있는 경우에는 Radical Oxygen을 이용하여 해결한다. (이는 홀전자로 인해 매우 큰 반응성을 가진다)

Furnace의 경우 기계적으로 복잡한 것은 없으며 중요한 것은 압력, 온도와 같은 공정조건이 중요한다.

1) N+ Annealing: implantation 후에 진행되는 공정이다. 손상된 격자를 고온에서 회복시키는 과정이다. Dopant가 들어갔다고 해서 바로 활성화되는 것이 아닌 Annealing을 통해서 활성화가 된다.

다만 고온공정으로 인해 Dopant가 확산되는 문제가 있는데, 확산되는 것을 원하지 않을때에는

RTA(Rapid Thermal Annealing)을 이용하여 Plasma로 빠른시간에 온도를 올리고 냉각시키는 방식을 이용한다.

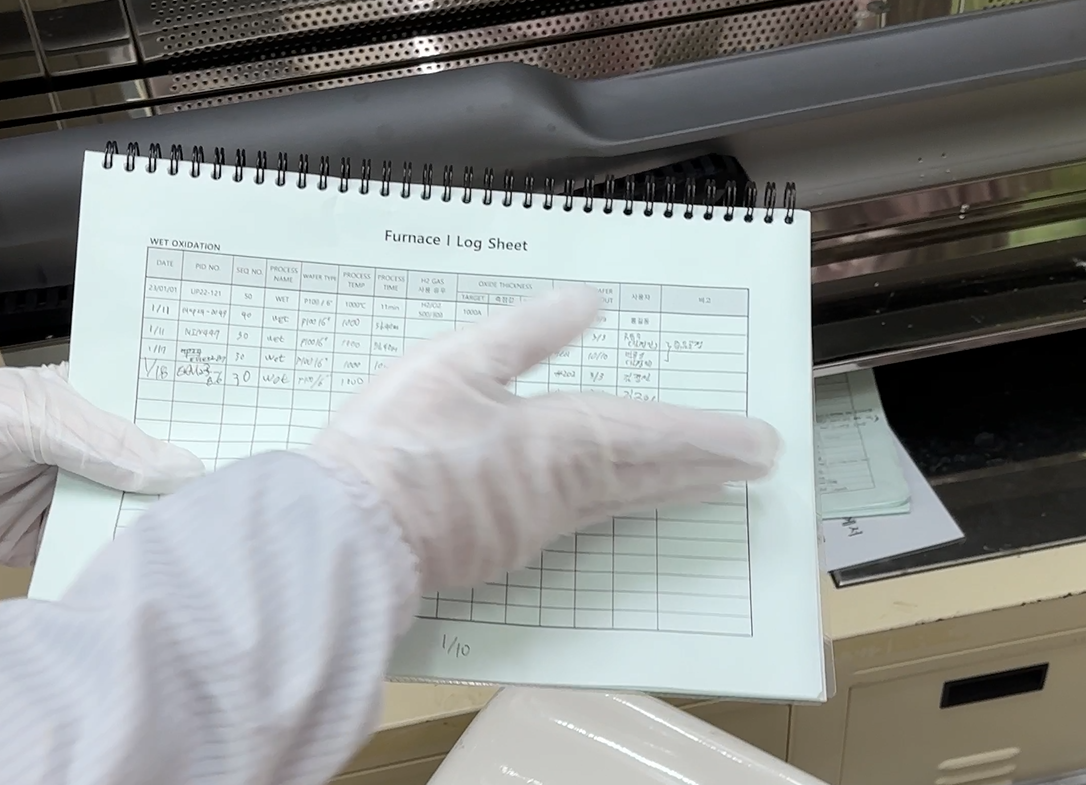

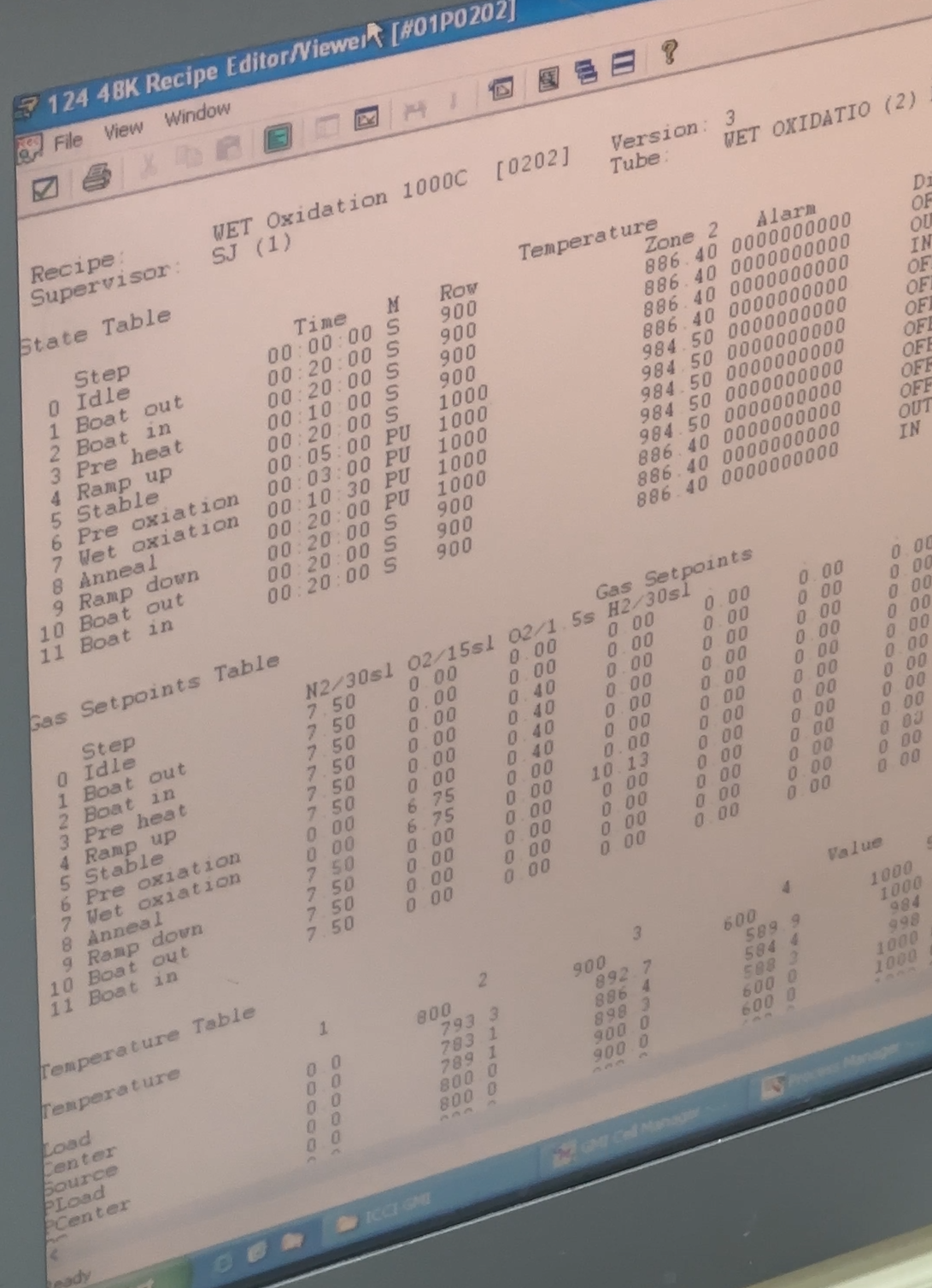

2) Wet Oxidation: O2와 H2 gas 모두 사용하며 여기서 사용되는 N2 gas는 압력을 조절하여 외부체의 유입을 막는다

보통 Deal-Grove Model에 따라서 성장하지만 이를 직접 계산하지 않고 이전 사용자의 Log Sheet을 참고하여 조건을 결정한다.

실제로 컴퓨터 내에서 레시피를 확인할 수 있다.

4. Inspection

Wafer Cleaning을 진행하고 Furnace로 Oxidation까지 마쳤다면 Inspection을 진행해서 Wafer가 원하는 수준의 Oxidation이 되었는지 확인해야 한다.

산화막의 성질을 평가하는 Parameter는 다음과 같다.

- Thickness

- Reflection index

- Density

- Pin hole

- Etch rate

- Breakdown Field

그 중 우리가 시행했던 Thickness Measurement를 설명하겠다.

분광반사율을 활용한 박막측정 방식으로는 Ellipsometer와 Nanospec이 존재하며

이들은 조작이 간단하고 Wafer에 손상을 주지 않지만 얇은 복수의 박막층 두께를 측정하는데에 부정확하다.

전자빔을 활용한 박막측정 방식으로는 Scanning Electron Microscopy(SEM)과 Transmission Electron Microscopy(TEM)이 존재하며 TEM의 경우 FIB를 통한 별도의 sample을 제작해야 하며 측정후 공정 진행이 불가능하고 높은 비용이 요구되는 대신 얇은 복수박막에 대한 정확한 두께 측정이 가능하다.

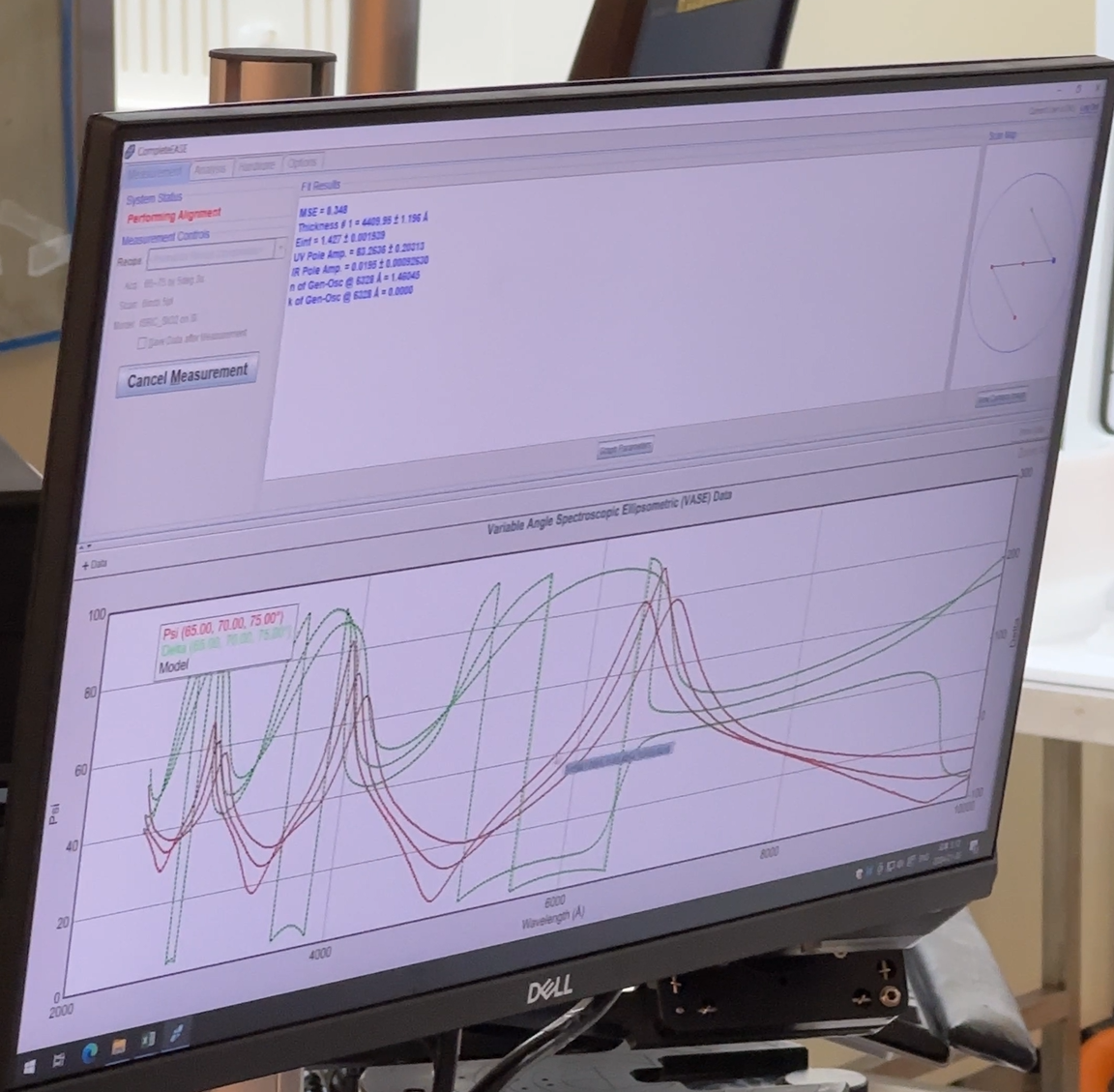

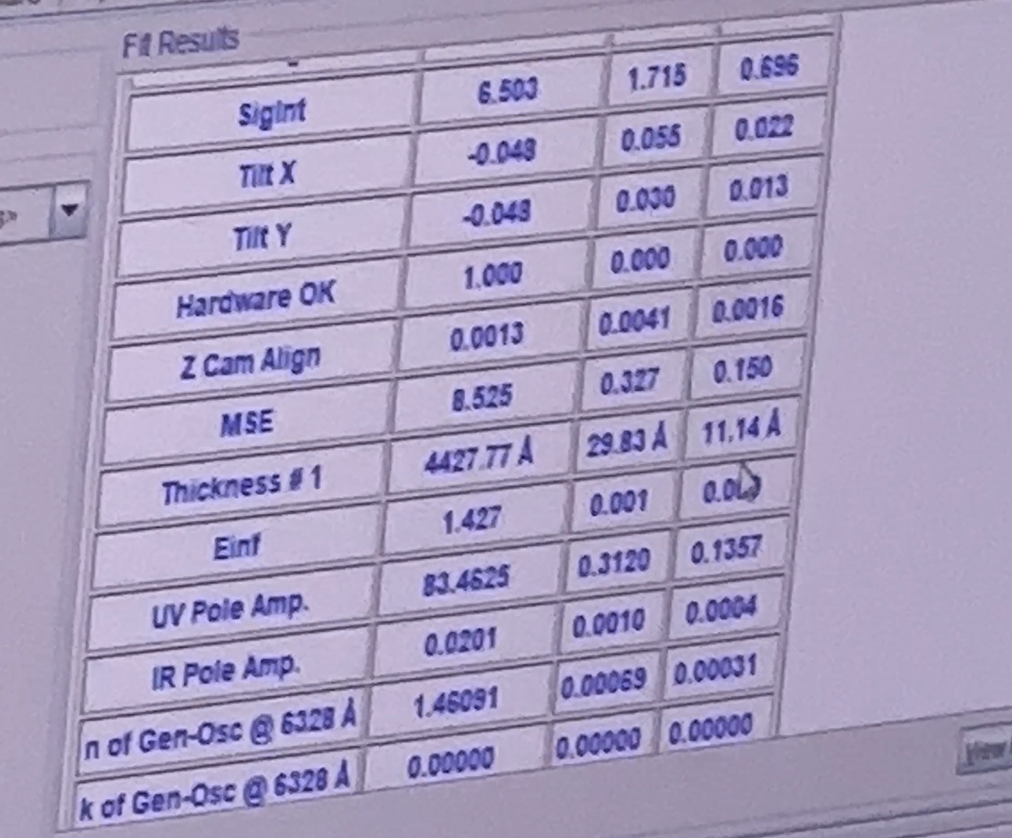

우리는 Ellipsometer를 이용하여 Data를 확인했는데, 하나의 Wafer 당 5개의 포인트를 지정하여 Thickness의 평균과 표준편차를 구하였다.

1) Furnace로 Oxiation을 진행한 Wafer를 꺼내준다.

이때 기름막같이 Wafer가 무지개 빛을 띄면 망한것.

2) Ellipsometer에 Wafer를 올려준다. Wafer는 진공이 가해지는 Plate에 놓여지게 되며 고정된다.

3개의 각도(65도/70도/75도)로 측정이 되며 각 변수마다 3개의 그래프가 나타나게 된다.

3) 위에 있는 수치뿐만 아니라 그래프가 피팅이 잘 되었는지를 확인해봐야 한다.

밑에 있는 박막이 무엇인지에 따라 영향을 많이 받으며 너무 두꺼울 경우 측정이 잘되지 않는다.

이러한 경우 레시피를 다시 바꿔주어야 하는 번거로움이 있다.

4) 측정이 종료되면 다음과 같은 데이터가 나온다

두께가 4400Å이며 표준편차는 11 Å이고 1나노미터 정도 울퉁불퉁함을 알 수 있다.

이렇게 Inspection 까지 끝내면 Oxidation 공정이 끝났다고 할 수 있다.

물론 Inspection에서 불합격 판정을 받으면 다시 되돌아가야 한다.

다음으로는 Lithography 공정을 기술하려고 한다.

'STUDY > Semiconductor' 카테고리의 다른 글

| 서울대학교 반도체 공동연구소 공정실습: Photolithography Process Part. 1 (0) | 2024.03.16 |

|---|---|

| 서울대학교 반도체 공동연구소 공정실습 : Oxidation Process part. 1 (0) | 2024.03.09 |

| ADVANTEST KOREA ATK T2000 Training (4) | 2024.02.04 |

| SEMICON KOREA 2024 Meet The Experts 참여 후기 (0) | 2024.02.04 |